# Juego de Instrucciones

# **<u>Índice</u>**

| Introducción                                                              | 5  |

|---------------------------------------------------------------------------|----|

| ADC - Suma con Acarreo                                                    | 6  |

| ADD - Suma sin Acarreo                                                    |    |

| AIS – Suma el valor Inmediato al Puntero de Pila (con signo)              | 8  |

| AIX - Suma el Valor Inmediato al Registro de índice (con signo)           | 9  |

| AND - AND Lógico                                                          | 10 |

| ASL - Desplazamiento Aritmético a la Izquierda                            |    |

| ASR - Desplazamiento Aritmético a la Derecha                              |    |

| BCC - Bifurcación si se pone a 0 el Acarreo                               | 13 |

| BCLR n - Pone a 0 un Bit en la Memoria                                    |    |

| BCS - Bifurcación si el Acarreo es 1                                      |    |

| BEQ - Bifurcación si es Igual                                             |    |

| $\pmb{BGE}$ - Bifurcación si es Mayor que o Igual a (operandos con signo) |    |

| BGT - Bifurcación si es Mayor que (operandos con signo)                   | 18 |

| BHCC - Bifurcación si Medio Acarreo es 0                                  | 19 |

| BHCC - Bifurcación si Medio Acarreo es 0                                  | 19 |

| BHCS - Bifurcación si Medio Acarreo es 1                                  | 20 |

| BHI - Bifurcación si es Mayor                                             | 21 |

| BHS - Bifurcación si es Mayor o Igual                                     | 22 |

| BIH - Bifurcación si el pin de Interrupción está a 1                      | 23 |

| BIL - Bifurcación si el Pin de Interrupción está a 0                      | 24 |

| BIT - Bit de Prueba de la Memoria con el Acumulador                       | 25 |

| $\pmb{BGE}$ - Bifurcación si es Mayor que o Igual a (operandos con signo) | 26 |

| BGT - Bifurcación si es Mayor que (operandos con signo)                   | 27 |

| BLE - Bifurcación si es Menor que o Igual a (Operandos con signo)         |    |

| BLO - Bifurcación si es más Menor                                         |    |

| BLS - Bifurcación si es Menor o Igual                                     |    |

| BLT - Bifurcación si es Menor que (Operandos con signo) | 31 |

|---------------------------------------------------------|----|

| BMC - Bifurcación si la Máscara de Interrupción es 0    | 32 |

| BMI - Bifurcación si es Menor                           |    |

| BMS - Bifurcación si la Máscara de Interrupción es 1    | 34 |

| BNE - Bifurcación si no es Igual                        | 35 |

| BPL - Bifurcación si es Positivo                        |    |

| BRA - Bifurcación Incondicional                         |    |

| BRCLR n - Bifurcación si el Bit n es Cero               |    |

| BRN - Nunca Bifurcación                                 |    |

| BRSET n - Bifurcación si el Bit n es 1                  |    |

| BSET n - Pone a 1 el Bit en la Memoria                  |    |

| BSR - Bifurcación a Subrutina                           | 42 |

| CBEQ - Compara y Bifurca si es Igual                    | 43 |

| CBEQA - Compara A con Inmediato, Bifurca si es Igual    | 44 |

| CBEQX - Compara X con Inmediato, Bifurca si es Igual    | 45 |

| CLC - Pone a Cero el Bit de Acarreo                     | 46 |

| CLI - Pone a Cero el Bit de Máscara de Interrupción     | 47 |

| CLR - Pone a Cero                                       | 48 |

| CLRH - Borra la parte alta del Registro de Índice (H)   | 49 |

| CMP - Compara el Acumulador con la Memoria              | 50 |

| COM - Complemento                                       | 51 |

| CPHX - Compara el Registro de Índice con la Memoria     | 52 |

| CPX - Compara el Registro de Índice con la Memoria      | 53 |

| DAA - Ajuste Decimal del Acumulador                     | 54 |

| DBNZ - Decrementa y Bifurca si no es Cero               |    |

| DEC - Decrementa                                        |    |

| DIV - Divide                                            |    |

| EOR - OR-Exclusiva de la Memoria con el Acumulador      |    |

| INC - Incrementa                                        | 59 |

| JMP - Salto                                                  | 60 |

|--------------------------------------------------------------|----|

| JSR - Salto a Subrutina                                      |    |

| LDA - Carga el Acumulador desde la Memoria                   | 62 |

| LDHX - Carga el Registro de Índice con la Memoria            | 63 |

| LDX - Carga el Registro de Índice desde la Memoria           | 64 |

| LSL - Desplazamiento Lógico a la Izquierda                   | 65 |

| LSR - Desplazamiento Lógico a la Derecha                     | 66 |

| MOV - Mueve                                                  | 67 |

| MUL - Multiplicación Sin Signo                               | 68 |

| NEG - Negado                                                 | 69 |

| NOP - No Operación                                           | 70 |

| NSA - Cambia los "nibbles" del Acumulador                    | 71 |

| ORA - OR-Inclusiva                                           | 72 |

| PSHA - Pone el Acumulador en la Pila                         | 73 |

| PSHH - Pone la parte alta del Registro Índice (H) en la Pila | 74 |

| PSHX - Pone la parte baja del Registro Índice (X) en la Pila | 75 |

| PULA - Saca el Acumulador de la Pila                         | 76 |

| PULH - Saca la parte alta del Registro Índice (H) de la Pila | 77 |

| PULX - Saca la parte baja del Registro Índice (H) de la Pila | 78 |

| ROL - Rotación a la Izquierda por Acarreo                    | 79 |

| ROR - Rotación a la Derecha por Acarreo                      | 80 |

| RSP - Reset del Puntero de Pila                              |    |

| RTI - Retorno de la Interrupción                             |    |

| RTS - Retorno de Subrutina                                   | 83 |

| SBC - Subtracción con Acarreo                                | 84 |

| SEC - Pone a 1 el bit de Acarreo                             | 85 |

| SEI - Pone a 1 el Bit de la Máscara de Interrupción          |    |

| STA - Guarda el Acumulador en la Memoria                     | 87 |

| STHX - Guarda el Registro de Índice                          | 88 |

| STOP - Habilita la IRQ y Para el Oscilador                        | 89  |

|-------------------------------------------------------------------|-----|

| STX - Guarda el Registro de Índice X en la Memoria                | 90  |

| SUB - Substracción                                                | 91  |

| SWI - Interrupción por Software                                   | 92  |

| STHX - Guarda el Registro de Índice                               | 93  |

| TAX - Transfiere el Acumulador al Registro de Índice              | 94  |

| TPA - Transfiere el Registro de Código de Condición al Acumulador | 95  |

| TST - Prueba para Negativo o Cero                                 | 96  |

| TSX - Transfiere el Puntero de Pila al Registro de Índice         | 97  |

| TXA - Transfiere el Registro de Índice al Acumulador              | 98  |

| TXS - Transfiere el Registro de Índice al Puntero de Pila         | 99  |

| WAIT - Habilita la Interrupción, Para el Procesador               | 100 |

#### Introducción

(rel)

Esta sección contiene información detallada de todas las instrucciones del 68HC08. Las instrucciones están puestas por orden alfabético incluyendo los mnemónicos, para una localización más fácil. En las definiciones se usan las nomenclaturas siguientes:

```

(a) Operandos

= Contenidos de Registro o Posición de Memoria Mostrados entre Paréntesis

()

= Está Cargado con (Lee: coge)

= se Saca de la Pila

= se Guarda en la Pila

= AND Booleana

= Suma Aritmética (Excepto donde se usó como OR Inclusiva en la fórmula Booleana)

\oplus

= OR Exclusiva Booleana

X

= Multiplica

= Encadena

= Negado (Complemento a Dos)

(b) Registros de la CPU

ACCA = Acumulador

= Registro de Código de Condición

CCR

X

= Registro de Índice

PC

= Contador de Programa

= Contador de Programa, Orden más Alto (los 8 bits más significativos)

PCH

= Contador de Programa, Orden más Bajo (los 8 bits menos significativos)

PCL

SP

= Puntero de Pila

(c) Memoria y Direccionamiento

= Una posición de memoria o datos absolutos, dependiendo del modo de direccionamiento

= Desplazamiento Relativo; por ejemplo, el número complemento a dos guardado en el último

Rel

byte de código de código máquina que corresponde a una instrucción de bifurcación

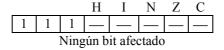

(d) Bits del Registro de Código de Condición (CCR)

= Medio Acarreo, Bit 4

= Máscara de Interrupción, Bit 3

Ι

Ν

= Indicador de Negativo, Bit 2

Z

= Indicador de Cero, Bit 1

C

= Acarreo (Carry/Borrow), Bit 0

(e) Bit de Estado ANTES de la Ejecución (n = 7, 6, 5...0)

= Bit n del registro ACCA

= Bit n del registro X

Xn

= Bit n del registro M

Mn

(f) Bit de estado DESPUÉS de la ejecución

= Bit n del Resultado (n = 7, 6, 5...0)

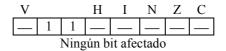

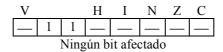

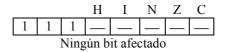

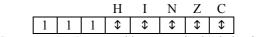

(g) Actividad Resumen del CCR, símbolos utilizados

= Bit no Afectado

0

= Bit Forzado a 0

1

= Bit Forzado a 1

1

= Bit Puesto 0 o a 1 según los Resultados de la Operación

(h) Anotación utilizada del Código Máquina

= 8 bits más bajos de una Dirección Directa $0000-$00FF; Byte Alto asumido para ser $0000

= Los 8 Bits más Altos de un Desplazamiento de 16 bits

ee

= Los 8 Bits más Bajos de un Desplazamiento de 16 bits o de 8-Bits

ff

= Un Byte de Datos Inmediato

ii

= El Byte más Alto de los 16-Bits de una Dirección Extendida

= El Byte más Bajo de los 16-Bits de una Dirección Extendida

= Desplazamiento Relativo

rr

(i) Anotación de forma de Fuente

= Operando; Uno o Dos Bytes que dependen del Modo de Direccionamiento

(opr)

= Desplazamiento Relativo Usado en instrucciones de Bifurcación y de Manipulación de Bit

```

### **ADC** - Suma con Acarreo

Operación:  $ACCA \leftarrow (ACCA) + (M) + (C)$

**Descripción:** Suma los contenidos del bit C a la suma de los contenidos del registro ACCA y del registro M, pone el resultado en el registro ACCA.

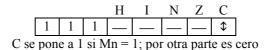

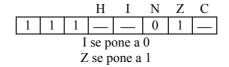

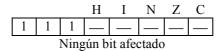

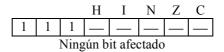

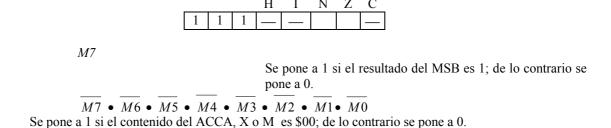

#### Códigos de condición y Formula Boleana

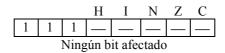

|   |   |   | Η         | I | N         | Z         | C  |

|---|---|---|-----------|---|-----------|-----------|----|

| 1 | 1 | 1 | <b>\$</b> | _ | <b>\$</b> | <b>\$</b> | \$ |

**H**  $A3 \bullet M3 + M3 \bullet \overline{R3} + \overline{R3} \bullet A3$

Se pone a 1 si había un acarreo del bit 3; de lo contrario se pone a 0.

N *R7*

Se pone a 1 si el resultado del MSB es 1; de lo contrario se pone a 0.

**Z**  $\overline{R7} \bullet \overline{R6} \bullet \overline{R5} \bullet \overline{R4} \bullet \overline{R3} \bullet \overline{R2} \bullet \overline{R1} \bullet \overline{R0}$

Se pone a 1 si todos los bits del resultado se ponen a 0; de lo contrario se pone a 0.

$\mathbf{C} \qquad \qquad A7 \bullet M7 + M7 \bullet \overline{R7} + \overline{R7} \bullet A7$

Se pone a 1 si había un acarreo del resultado del MSB; de lo contrario se pone a 0.

| Código      | Modo de          | Códi               | Ciclos |    |   |

|-------------|------------------|--------------------|--------|----|---|

| Fuente      | Direccionamiento | Opcode Operando(s) |        | 1  |   |

| ADC (opr)   | IMM              | A9                 | ii     |    | 2 |

| ADC (opr)   | DIR              | В9                 | dd     |    | 3 |

| ADC (opr)   | EXT              | C9                 | hh     | 11 | 4 |

| ADC ,X      | IX               | F9                 |        |    | 3 |

| ADC (opr),X | IX1              | E9                 | ff     |    | 4 |

| ADC (opr),X | IX2              | D9                 | Ee     | ff | 5 |

## ADD - Suma sin Acarreo

Operación:  $ACCA \leftarrow (ACCA) + (M)$

**Descripción:** Suma los contenidos de M a los contenidos de ACCA y pone el resultado en ACCA.

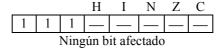

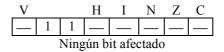

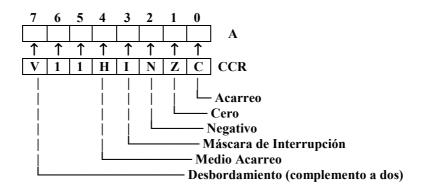

#### Códigos de condición y Formula Boleana

|   |   |   | Η         | I | N         | Z         | C        |

|---|---|---|-----------|---|-----------|-----------|----------|

| 1 | 1 | 1 | <b>\$</b> |   | <b>\$</b> | <b>\$</b> | <b>+</b> |

$\mathbf{H} \qquad \qquad A3 \bullet M3 + M3 \bullet \overline{R3} + \overline{R3} \bullet A3$

Se pone a 1 si había un acarreo del bit 3; de lo contrario se pone a 0.

N *R7*

Se pone a 1 si el resultado MSB es 1; de lo contrario se pone a 0.

**Z**  $\overline{R7} \bullet \overline{R6} \bullet \overline{R5} \bullet \overline{R4} \bullet \overline{R3} \bullet \overline{R2} \bullet \overline{R1} \bullet \overline{R0}$

Se pone a 1 si todos los bits del resultado se ponen a 0; de lo contrario se pone a 0.

C  $A7 \bullet M7 + M7 \bullet \overline{R7} + \overline{R7} \bullet A7$

Se pone a 1 si había un acarreo del resultado del MSB; de lo contrario se pone a 0.

| Código      | Modo de          | Código Máquina |             |    | Ciclos |

|-------------|------------------|----------------|-------------|----|--------|

| Fuente      | Direccionamiento | Opcode         | Operando(s) |    |        |

| ADD (opr)   | IMM              | AB             | ii          |    | 2      |

| ADD (opr)   | DIR              | BB             | dd          |    | 3      |

| ADD (opr)   | EXT              | CB             | hh          | 11 | 4      |

| ADD ,X      | IX               | FB             |             |    | 3      |

| ADD (opr),X | IX1              | EB             | ff          |    | 4      |

| ADD (opr),X | IX2              | DB             | ee          | ff | 5      |

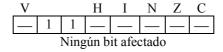

## AIS - Suma el valor Inmediato al Puntero de Pila (con signo)

Operación:  $SP \leftarrow (SP) + (16 \ll M)$

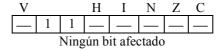

**Descripción:** Suma el operando inmediato al Stack pointer (SP). El valor inmediato es un operando de 8 bits complemento a dos con signo. El operando de 8 bits es extendido a 16 bits con signo, anterior a la suma. La instrucción AIS se puede usar para crear y quitar un 'buffer' de la zona del stack, que se usa para guardar temporalmente las variables.

Esta instrucción no afecta ningún bit de código de condición, para que la información de estado se pueda pasar a/o de una subrutina o función C y asignando o no el espacio para las variables locales que no perturbarán esa información de estado.

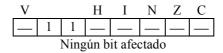

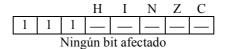

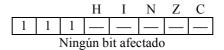

#### Códigos de condición y Formula Boleana

| Código   | Modo de          | Cód    | HC08  |         |        |

|----------|------------------|--------|-------|---------|--------|

| Fuente   | Direccionamiento | Opcode | Opera | indo(s) | Ciclos |

| AIS #opr | IMM              | A7     | ii    | ii      | 2      |

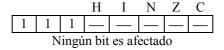

## AIX - Suma el Valor Inmediato al Registro de índice (con signo)

Operación:  $H:X \leftarrow (H:X) + (16 \ll M)$

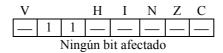

**Descripción:** Suma el operando inmediato al Registro de índice de 16 bits, formado por la concatenación del registro H y X. El operando inmediato es un offset de 8 bits complemento a dos con signo. El operando de 8 bits es extendido a 16 bits con signo anterior a la suma.

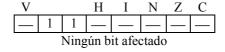

Esta instrucción no afecta ningún bit de código de condición, para que los cálculos del puntero del registro de índice no perturbará el código circundante que puede consultar de forma segura el estado de los bits de estado del CCR..

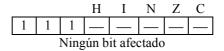

#### Códigos de condición y Formula Boleana

| Código   | Modo de                 | Cód    | HC08        |        |

|----------|-------------------------|--------|-------------|--------|

| Fuente   | <b>Direccionamiento</b> | Opcode | Operando(s) | Ciclos |

| AIX #opr | IMM                     | AF     | ii          | 2      |

## AND - AND Lógico

Operación:  $ACCA \leftarrow (ACCA) \cdot (M)$

**Descripción:** Realiza un AND lógico entre el contenido ACCA y M, pone el resultado en ACCA. (Cada bit del ACCA después de la operación será un AND lógico de los correspondientes bits de M y ACCA antes de la operación.)

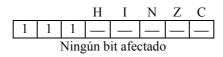

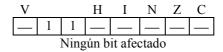

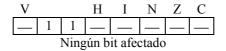

#### Códigos de condición y Formula Boleana

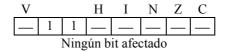

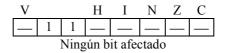

|   |   |   | Η | I | N         | Z         | C |

|---|---|---|---|---|-----------|-----------|---|

| 1 | 1 | 1 |   |   | <b>\$</b> | <b>\$</b> |   |

N R7

Se pone a 1 si el resultado MSB es 1; de lo contrario se pone a 0.

**Z**  $\overline{R7} \bullet \overline{R6} \bullet \overline{R5} \bullet \overline{R4} \bullet \overline{R3} \bullet \overline{R2} \bullet \overline{R1} \bullet \overline{R0}$

Se pone a 1 si todos los bits del resultado se ponen a 0; de lo contrario se pone a 0.

| Código Fuente | Modo de          | Código Máquina |             |    | Ciclos |

|---------------|------------------|----------------|-------------|----|--------|

|               | Direccionamiento | Opcode         | Operando(s) |    |        |

| AND (opr)     | IMM              | A4             | ii          |    | 2      |

| AND (opr)     | DIR              | B4             | dd          |    | 3      |

| AND (opr)     | EXT              | C4             | hh          | 11 | 4      |

| AND ,X        | IX               | F4             |             |    | 3      |

| AND (opr),X   | IX1              | E4             | ff          | •  | 4      |

| AND (opr),X   | IX2              | D4             | ee          | ff | 5      |

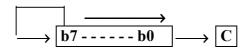

## ASL - Desplazamiento Aritmético a la Izquierda

(Lo mismo que la instrucción LSL)

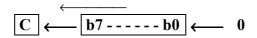

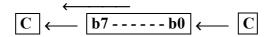

#### Operación:

**Descripción:** Desplaza un lugar a la izquierda todos los bits del ACCA, X o M. El Bit 0 está cargado con un cero. El bit C en el CCR está cargado con el bit más significativo de ACCA, X o M.

#### Códigos de condición y Formula Boleana

$\mathbf{N}$

Se pone a 1 si el resultado MSB es 1; de lo contrario se pone a 0.

**Z**  $\overline{R7} \bullet \overline{R6} \bullet \overline{R5} \bullet \overline{R4} \bullet \overline{R3} \bullet \overline{R2} \bullet \overline{R1} \bullet \overline{R0}$

Se pone a 1 si todos los bits del resultado se ponen a 0; de lo contrario se pone a 0.

**C** b7

Se pone a 1 si antes del desplazamiento el valor MSB del valor desplazado era 1; de lo contrario se pone a 0.

| Código Fuente | Modo de Código Máquina |        |             | Ciclos |

|---------------|------------------------|--------|-------------|--------|

|               | Direccionamiento       | Opcode | Operando(s) |        |

| ASLA          | INH (A)                | 48     |             | 3      |

| ASLX          | INH (X)                | 58     |             | 3      |

| ASL (opr)     | DIR                    | 38     | dd          | 5      |

| ASL           | IX                     | 78     |             | 5      |

| ASL (opr),X   | IX1                    | 68     | ff          | 6      |

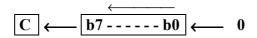

## ASR - Desplazamiento Aritmético a la Derecha

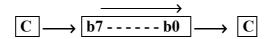

#### Operación:

**Descripción:** Desplaza todos los bits un lugar a la derecha del ACCA, X o M. El Bit 7 se mantiene constante. El Bit 0 está cargado en el Bit C del CCR. Esta operación divide eficazmente un valor complemento a dos por dos sin cambiar su signo. El bit de acarreo se puede usar para redondear el resultado.

#### Códigos de condición y Formula Boleana

$$N$$

$R7$

Se pone a 1 si el resultado MSB es 1; de lo contrario se pone a 0.

$$\overline{R7} \bullet \overline{R6} \bullet \overline{R5} \bullet \overline{R4} \bullet \overline{R3} \bullet \overline{R2} \bullet \overline{R1} \bullet \overline{R0}$$

Se pone a 1 si todos los bits del resultado se ponen a 0; de lo contrario se pone a 0.

Se pone a 1 si antes del desplazamiento, el valor LSB del valor desplazado era 1; de lo contrario se pone a 0.

| Código      | Modo de          | Códig  | Ciclos      |   |

|-------------|------------------|--------|-------------|---|

| Fuente      | Direccionamiento | Opcode | Operando(s) |   |

| ASRA        | INH (A)          | 47     |             | 3 |

| ASRX        | INH (X)          | 57     |             | 3 |

| ASR (opr)   | DIR              | 37     | dd          | 5 |

| ASR ,X      | IX               | 77     |             | 5 |

| ASR (opr),X | IX1              | 67     | ff          | 6 |

## BCC - Bifurcación si se pone a 0 el Acarreo

(Lo mismo que la instrucción BHS)

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si (C) = 0

**Descripción:** Prueba el estado del bit C en el CCR y provoca una bifurcación si C está a 0. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Ciclos      |   |

|-----------|------------------|--------|-------------|---|

| Fuente    | Direccionamiento | Opcode | Operando(s) |   |

| BCC (rel) | REL              | 24     | rr          | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Compleme         | entario | Bifurcación | Comentario    |

|--------------|-----------|-----------|--------|------------------|---------|-------------|---------------|

| r > m        | C + Z = 0 | BHI       | 22     | r ≤ m            | BLS     | 23          | Sin signo     |

| r ≥ m        | C = 0     | BHS/BCC   | 24     | r < m            | BLO/BCS | 25          | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | r≠m              | BNE     | 26          | Sin signo     |

| r ≤ m        | C + Z = 1 | BLS       | 23     | r > m            | BHI     | 22          | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | R≥m              | BHS/BCC | 24          | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo      | BCC     | 24          | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0            | BNE     | 26          | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más              | BPL     | 2A          | Simple        |

| I            | I = 1     | BMS       | 2D     | I                | BMC     | 2C          | Simple        |

| Enmascarable |           |           |        | Enmascarable = 0 |         |             |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio         | BHCC    | 28          | Simple        |

| Acarreo      |           |           |        | Acarreo          |         |             | _             |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo         | BIL     | 2E          | Simple        |

| Siempre      |           | BRA       | 20     | Nunca            | BRN     | 21          | Incondicional |

r = registro (ACCA o X); m = operando memoria

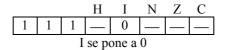

### BCLR n - Pone a 0 un Bit en la Memoria

Operación:  $Mn \leftarrow 0$

**Descripción:** Pone a 0 el Bit n (n = 7, 6, 5. . 0) en la posición M. Todos los otros bits en M no están afectados. M puede ser cualquier posición de la RAM o dirección del registro de E/S en el área de memoria de \$0000 a \$00FF (por ejemplo, en el modo de direccionamiento directo se usa para especificar la dirección del operando).

#### Códigos de condición y Formula Boleana

| Código       | Modo de          | Código | o Máquina   | Ciclos |

|--------------|------------------|--------|-------------|--------|

| Fuente       | Direccionamiento | Opcode | Operando(s) |        |

| BCLR 0,(opr) | DIR (bit 0)      | 11     | dd          | 5      |

| BCLR 1,(opr) | DIR (bit 1)      | 13     | dd          | 5      |

| BCLR 2,(opr) | DIR (bit 2)      | 15     | dd          | 5      |

| BCLR 3,(opr) | DIR (bit 3)      | 17     | dd          | 5      |

| BCLR 4,(opr) | DIR (bit 4)      | 19     | dd          | 5      |

| BCLR 5,(opr) | DIR (bit 5)      | 1B     | dd          | 5      |

| BCLR 6,(opr) | DIR (bit 6)      | 1D     | dd          | 5      |

| BCLR 7,(opr) | DIR (bit 7)      | 1F     | dd          | 5      |

### BCS - Bifurcación si el Acarreo es 1

(Lo mismo que la instrucción BLO)

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si(C) = 1

**Descripción:** Prueba el estado del bit C en el CCR y provoca una bifurcación, si C está a 1. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Ciclos      |   |

|-----------|------------------|--------|-------------|---|

| Fuente    | Direccionamiento | Opcode | Operando(s) |   |

| BCS (rel) | REL              | 25     | rr          | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Complem      | entario | Bifurcació | Comentario    |

|--------------|-----------|-----------|--------|--------------|---------|------------|---------------|

|              |           |           |        |              |         | n          |               |

| r > m        | C + Z = 0 | BHI       | 22     | $R \leq m$   | BLS     | 23         | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | R < m        | BLO/BCS | 25         | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m        | BNE     | 26         | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m        | BHI     | 22         | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$    | BHS/BCC | 24         | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo  | BCC     | 24         | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0        | BNE     | 26         | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más          | BPL     | 2A         | Simple        |

| I            | I = 1     | BMS       | 2D     | I            | BMC     | 2C         | Simple        |

| Enmascarable |           |           |        | Enmascarable |         |            |               |

|              |           |           |        | = 0          |         |            |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio     | BHCC    | 28         | Simple        |

| Acarreo      |           |           |        | Acarreo      |         |            |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo     | BIL     | 2E         | Simple        |

| Siempre      | _         | BRA       | 20     | Nunca        | BRN     | 21         | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BEQ - Bifurcación si es Igual

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si(Z) = 1

**Descripción**: Prueba el estado del bit Z en el CCR y provoca una bifurcación si Z está a 1. Siguiendo a una instrucción CMP o SUB, la instrucción BEQ causará una bifurcación si los argumentos son iguales. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Ciclos      |   |

|-----------|------------------|--------|-------------|---|

| Fuente    | Direccionamiento | Opcode | Operando(s) |   |

| BEQ (rel) | REL              | 27     | rr          | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Compleme     | entario | Bifurcación | Comentario    |

|--------------|-----------|-----------|--------|--------------|---------|-------------|---------------|

| r > m        | C + Z = 0 | BHI       | 22     | R ≤ m        | BLS     | 23          | Sin signo     |

| r ≥ m        | C = 0     | BHS/BCC   | 24     | R < m        | BLO/BCS | 25          | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m        | BNE     | 26          | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m        | BHI     | 22          | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$    | BHS/BCC | 24          | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo  | BCC     | 24          | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0        | BNE     | 26          | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más          | BPL     | 2A          | Simple        |

| I            | I = 1     | BMS       | 2D     | I            | BMC     | 2C          | Simple        |

| Enmascarable |           |           |        | Enmascarable |         |             |               |

|              |           |           |        | = 0          |         |             |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio     | BHCC    | 28          | Simple        |

| Acarreo      |           |           |        | Acarreo      |         |             |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo     | BIL     | 2E          | Simple        |

| Siempre      |           | BRA       | 20     | Nunca        | BRN     | 21          | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BGE - Bifurcación si es Mayor que o Igual a (operandos con signo)

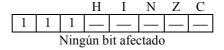

Operación:  $PC \leftarrow (PC) + \$0002 + rel$   $si(N \oplus V) = 0$

Por ejemplo, si (A) (M) (números complemento a dos con signo)

**Descripción:** Si la instrucción BGE se ejecuta inmediatamente después de la ejecución de una instrucción de comparación o de substracción, la bifurcación ocurre si y sólo si, el número complemento a dos representado por el registro interno apropiado (A, X o H:X) era mayor que o igual, al número complemento a dos representado por M.

#### Códigos de condición y Formula Boleana

| Código  | Modo de          | Cód    | HC08        |        |

|---------|------------------|--------|-------------|--------|

| Fuente  | Direccionamiento | Opcode | Operando(s) | Ciclos |

| BGE opr | REL              | 90     | rr          | 3      |

## BGT - Bifurcación si es Mayor que (operandos con signo)

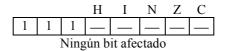

Operación:  $PC \leftarrow (PC) + \$0002 + rel$   $si Z \mid (N \oplus V) = 0$

Por ejemplo, si (A) > (M) (números complemento a dos con signo)

**Descripción:** Si la instrucción BGT se ejecuta inmediatamente después de la ejecución de una instrucción CMP, CPX, CPHX o SUB, la bifurcación ocurre si y sólo si, el número complemento a dos representado por el registro interno apropiado (A, X o H:X) era mayor que el número complemento a dos, representado por M.

#### Códigos de condición y Formula Boleana

| Código  | Modo de          | Cód    | HC08        |        |

|---------|------------------|--------|-------------|--------|

| Fuente  | Direccionamiento | Opcode | Operando(s) | Ciclos |

| BGT opr | REL              | 92     | rr          | 3      |

## BHCC - Bifurcación si Medio Acarreo es 0

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si(H) = 0

**Descripción**: Prueba el estado del bit H en el CCR y provoca una bifurcación si H está a 0. Esta instrucción se usa en algoritmos que involucran números BCD. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código     | Modo de          | Código | Ciclos      |   |

|------------|------------------|--------|-------------|---|

| Fuente     | Direccionamiento | Opcode | Operando(s) |   |

| BHCC (rel) | REL              | 28     | rr          | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Compleme         | entario | Bifurcación | Comentario    |

|--------------|-----------|-----------|--------|------------------|---------|-------------|---------------|

| r > m        | C + Z = 0 | BHI       | 22     | $R \le m$        | BLS     | 23          | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | R < m            | BLO/BCS | 25          | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m            | BNE     | 26          | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m            | BHI     | 22          | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$        | BHS/BCC | 24          | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo      | BCC     | 24          | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0            | BNE     | 26          | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más              | BPL     | 2A          | Simple        |

| I            | I = 1     | BMS       | 2D     | I                | BMC     | 2C          | Simple        |

| Enmascarable |           |           |        | Enmascarable = 0 |         |             |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio         | BHCC    | 28          | Simple        |

| Acarreo      |           |           |        | Acarreo          |         |             |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo         | BIL     | 2E          | Simple        |

| Siempre      | _         | BRA       | 20     | Nunca            | BRN     | 21          | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BHCS - Bifurcación si Medio Acarreo es 1

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si(H) = 1

**Descripción:** Prueba el estado del bit H en el CCR y provoca una bifurcación si H está a 1. Esta instrucción se usa en algoritmos que involucran números BCD. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código     | Modo de          | Código | Máquina | Ciclos |

|------------|------------------|--------|---------|--------|

| Fuente     | Direccionamiento | Opcode |         |        |

| BHCS (rel) | REL              | 29     | rr      | 3      |

| Prueba       | Boole     | Mnemónico | Opcode | Compleme     | Complementario |    | Comentario    |

|--------------|-----------|-----------|--------|--------------|----------------|----|---------------|

| r > m        | C + Z = 0 | BHI       | 22     | R ≤ m        | BLS            | 23 | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | R < m        | BLO/BCS        | 25 | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m        | BNE            | 26 | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m        | BHI            | 22 | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$    | BHS/BCC        | 24 | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo  | BCC            | 24 | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0        | BNE            | 26 | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más          | BPL            | 2A | Simple        |

| I            | I = 1     | BMS       | 2D     | I            | BMC            | 2C | Simple        |

| Enmascarable |           |           |        | Enmascarable |                |    |               |

|              |           |           |        | = 0          |                |    |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio     | BHCC           | 28 | Simple        |

| Acarreo      |           |           |        | Acarreo      |                |    |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo     | BIL            | 2E | Simple        |

| Siempre      | _         | BRA       | 20     | Nunca        | BRN            | 21 | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BHI - Bifurcación si es Mayor

Operación:  $C \leftarrow (PC) + \$0002 + Rel$  Si(C) + (Z) = 0

por ejemplo, si (ACCA) > (M) (números binarios sin signo)

**Descripción:** Causa una bifurcación si se pone C y Z a 0. Si la instrucción BHl se ejecuta inmediatamente después de la ejecución de una instrucción CMP o SUB, ocurrirá la bifurcación si el número binario sin signo en ACCA es mayor que el número binario sin signo en M. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Máquina | Ciclos |

|-----------|------------------|--------|---------|--------|

| Fuente    | Direccionamiento | Opcode |         |        |

| BHI (rel) | REL              | 22     | rr      | 3      |

| Prueba           | Boole     | Mnemónico | Opcode | Compleme            | entario | Bifurcación | Comentario    |

|------------------|-----------|-----------|--------|---------------------|---------|-------------|---------------|

| r > m            | C + Z = 0 | BHI       | 22     | R ≤ m               | BLS     | 23          | Sin signo     |

| r ≥ m            | C = 0     | BHS/BCC   | 24     | R < m               | BLO/BCS | 25          | Sin signo     |

| r = m            | Z = 1     | BEQ       | 27     | R ≠ m               | BNE     | 26          | Sin signo     |

| r≤ m             | C + Z = 1 | BLS       | 23     | R > m               | BHI     | 22          | Sin signo     |

| r < m            | C = 1     | BLO/BCS   | 25     | $R \ge m$           | BHS/BCC | 24          | Sin signo     |

| Acarreo          | C = 1     | BCS       | 25     | Sin Acarreo         | BCC     | 24          | Simple        |

| r = 0            | Z = 1     | BEQ       | 27     | r ≠ 0               | BNE     | 26          | Simple        |

| Negativo         | N = 1     | BMI       | 2B     | Más                 | BPL     | 2A          | Simple        |

| I                | I = 1     | BMS       | 2D     | I                   | BMC     | 2C          | Simple        |

| Enmascarable     |           |           |        | Enmascarable = 0    |         |             |               |

| Medio<br>Acarreo | H = 1     | BHCS      | 29     | No Medio<br>Acarreo | ВНСС    | 28          | Simple        |

| IRQ Pin Alto     | _         | BIH       | 2F     | IRQ Bajo            | BIL     | 2E          | Simple        |

| Siempre          |           | BRA       | 20     | Nunca               | BRN     | 21          | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BHS - Bifurcación si es Mayor o Igual

(Lo mismo que la instrucción BCC)

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si (C) = 0

por ejemplo, si  $(ACCA) \ge (M)$  (números binarios sin signo)

**Descripción:** Si la instrucción BHS se ejecuta inmediatamente después de la ejecución de una instrucción CMP o SUB, la bifurcación ocurrirá si el número binario sin signo en ACCA era mayor o igual al número binario sin signo en M. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Código Máquina |   |  |  |  |

|-----------|------------------|--------|----------------|---|--|--|--|

| Fuente    | Direccionamiento | Opcode | Operando(s)    |   |  |  |  |

| BHS (rel) | REL              | 24     | rr             | 3 |  |  |  |

| Prueba       | Boole     | Mnemónico | Opcode | Compleme     | entario | Bifurcación | Comentario    |

|--------------|-----------|-----------|--------|--------------|---------|-------------|---------------|

| r > m        | C + Z = 0 | BHI       | 22     | R ≤ m        | BLS     | 23          | Sin signo     |

| r ≥ m        | C = 0     | BHS/BCC   | 24     | R < m        | BLO/BCS | 25          | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m        | BNE     | 26          | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m        | BHI     | 22          | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$    | BHS/BCC | 24          | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo  | BCC     | 24          | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0        | BNE     | 26          | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más          | BPL     | 2A          | Simple        |

| I            | I = 1     | BMS       | 2D     | I            | BMC     | 2C          | Simple        |

| Enmascarable |           |           |        | Enmascarable |         |             |               |

|              |           |           |        | = 0          |         |             |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio     | BHCC    | 28          | Simple        |

| Acarreo      |           |           |        | Acarreo      |         |             |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo     | BIL     | 2E          | Simple        |

| Siempre      |           | BRA       | 20     | Nunca        | BRN     | 21          | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BIH - Bifurcación si el pin de Interrupción está a 1

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si IRQ = 1

**Descripción**: Prueba el estado del pin de interrupción externa y provoca una bifurcación si el pin está en nivel alto. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Máquina | Ciclos |

|-----------|------------------|--------|---------|--------|

| Fuente    | Direccionamiento | Opcode |         |        |

| BIH (rel) | REL              | 2F     | rr      | 3      |

| Prueba       | Boole     | Mnemónico | Opcode | Compleme         | entario | Bifurcación | Comentario    |

|--------------|-----------|-----------|--------|------------------|---------|-------------|---------------|

| r > m        | C + Z = 0 | BHI       | 22     | $R \leq m$       | BLS     | 23          | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | R < m            | BLO/BCS | 25          | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m            | BNE     | 26          | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m            | BHI     | 22          | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$        | BHS/BCC | 24          | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo      | BCC     | 24          | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0            | BNE     | 26          | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más              | BPL     | 2A          | Simple        |

| I            | I = 1     | BMS       | 2D     | I                | BMC     | 2C          | Simple        |

| Enmascarable |           |           |        | Enmascarable = 0 |         |             |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio         | BHCC    | 28          | Simple        |

| Acarreo      |           |           |        | Acarreo          |         |             |               |

| IRQ Pin Alto |           | BIH       | 2F     | IRQ Bajo         | BIL     | 2E          | Simple        |

| Siempre      |           | BRA       | 20     | Nunca            | BRN     | 21          | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BIL - Bifurcación si el Pin de Interrupción está a 0

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si IRQ = 0

**Descripción:** Prueba el estado del pin de interrupción externa y provoca una bifurcación si el pin está en nivel bajo. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código             | Máquina | Ciclos |

|-----------|------------------|--------------------|---------|--------|

| Fuente    | Direccionamiento | Opcode Operando(s) |         |        |

| BIL (rel) | REL              | 2E                 | rr      | 3      |

| Prueba           | Boole     | Mnemónico | Opcode | Compleme            | entario | Bifurcación | Comentario    |

|------------------|-----------|-----------|--------|---------------------|---------|-------------|---------------|

| r > m            | C + Z = 0 | BHI       | 22     | R ≤ m               | BLS     | 23          | Sin signo     |

| r ≥ m            | C = 0     | BHS/BCC   | 24     | R < m               | BLO/BCS | 25          | Sin signo     |

| r = m            | Z = 1     | BEQ       | 27     | R ≠ m               | BNE     | 26          | Sin signo     |

| r≤ m             | C + Z = 1 | BLS       | 23     | R > m               | BHI     | 22          | Sin signo     |

| r < m            | C = 1     | BLO/BCS   | 25     | $R \ge m$           | BHS/BCC | 24          | Sin signo     |

| Acarreo          | C = 1     | BCS       | 25     | Sin Acarreo         | BCC     | 24          | Simple        |

| r = 0            | Z = 1     | BEQ       | 27     | r ≠ 0               | BNE     | 26          | Simple        |

| Negativo         | N = 1     | BMI       | 2B     | Más                 | BPL     | 2A          | Simple        |

| I                | I = 1     | BMS       | 2D     | I                   | BMC     | 2C          | Simple        |

| Enmascarable     |           |           |        | Enmascarable = 0    |         |             |               |

| Medio<br>Acarreo | H = 1     | BHCS      | 29     | No Medio<br>Acarreo | ВНСС    | 28          | Simple        |

| IRQ Pin Alto     |           | BIH       | 2F     | IRQ Bajo            | BIL     | 2E          | Simple        |

| Siempre          | _         | BRA       | 20     | Nunca               | BRN     | 21          | Incondicional |

r = registro (ACCA o X); m = operando memoria

### BIT - Bit de Prueba de la Memoria con el Acumulador

Operación: (ACCA) · (M)

**Descripción**: Realiza una comparación lógica AND de los contenidos de ACCA y M, y modifica de acuerdo el código de condición. No se alteran los contenidos de ACCA ni de M. (Cada bit del resultado AND lógico, serán los bits correspondientes de ACCA y M).

#### Códigos de condición y Formula Boleana

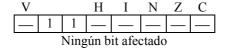

|   |   |   | Η | I | N         | Z         | C |

|---|---|---|---|---|-----------|-----------|---|

| 1 | 1 | 1 | _ |   | <b>\$</b> | <b>\$</b> |   |

N *R7*

Se pone a 1 si el resultado MSB es 1; de lo contrario se pone a 0.

**Z**  $\overline{R7} \bullet \overline{R6} \bullet \overline{R5} \bullet \overline{R4} \bullet \overline{R3} \bullet \overline{R2} \bullet \overline{R1} \bullet \overline{R0}$

Se pone a 1 si el resultado es \$00; de lo contrario se pone a 0.

| Código Fuente | Modo de          | Código Máquina |       | Ciclos |   |

|---------------|------------------|----------------|-------|--------|---|

|               | Direccionamiento | Opcode         | Opera | ndo(s) |   |

| BIT (opr)     | IMM              | A5             | ii    |        | 2 |

| BIT (opr)     | DIR              | B5             | dd    |        | 3 |

| BIT (opr)     | EXT              | C5             | hh    | 11     | 4 |

| BIT ,X        | IX               | F5             |       |        | 3 |

| BIT (opr),X   | IX1              | E5             | ff    |        | 4 |

| BIT (opr),X   | IX2              | D5             | Ee    | ff     | 5 |

## BGE - Bifurcación si es Mayor que o Igual a (operandos con signo)

Operación:  $PC \leftarrow (PC) + \$0002 + rel$   $si(N \oplus V) = 0$

Por ejemplo, si (A) (M) (números complemento a dos con signo)

**Descripción:** Si la instrucción BGE se ejecuta inmediatamente después de la ejecución de una instrucción de comparación o de substracción, la bifurcación ocurre si y sólo si, el número complemento a dos representado por el registro interno apropiado (A, X o H:X) era mayor que o igual, al número complemento a dos representado por M.

#### Códigos de condición y Formula Boleana

| Código  | Modo de                 | Cód | HC08        |        |

|---------|-------------------------|-----|-------------|--------|

| ruente  | Fuente Direccionamiento |     | Operando(s) | Ciclos |

| BGE opr | REL                     | 90  | rr          | 3      |

## BGT - Bifurcación si es Mayor que (operandos con signo)

Operación:  $PC \leftarrow (PC) + \$0002 + rel$  si  $Z \mid (N \oplus V) = 0$

Por ejemplo, si (A) > (M) (números complemento a dos con signo)

**Descripción:** Si la instrucción BGT se ejecuta inmediatamente después de la ejecución de una instrucción CMP, CPX, CPHX o SUB, la bifurcación ocurre si y sólo si, el número complemento a dos representado por el registro interno apropiado (A, X o H:X) era mayor que el número complemento a dos, representado por M.

#### Códigos de condición y Formula Boleana

| Código                  | Modo de | Cód    | HC08        |        |

|-------------------------|---------|--------|-------------|--------|

| Fuente Direccionamiento |         | Opcode | Operando(s) | Ciclos |

| BGT opr                 | REL     | 92     | rr          | 3      |

## BLE - Bifurcación si es Menor que o Igual a (Operandos con signo)

Operación:  $PC \leftarrow (PC) + \$0002 + rel$   $si Z \mid (N \oplus V) = 1$

Por ejemplo, si (A) (M) (números complemento a dos con signo)

**Descripción:** Si la instrucción BLE se ejecuta inmediatamente después de la ejecución de una instrucción CMP, CPX, CPHX o SUB, la bifurcación ocurre si y sólo si, el número complemento a dos representado por el registro interno apropiado (A, X o H:X) era menor que o igual al número complemento a dos representado por M.

#### Códigos de condición y Formula Boleana

| Código  | Modo de          | Cód    | HC08        |        |

|---------|------------------|--------|-------------|--------|

| Fuente  | Direccionamiento | Opcode | Operando(s) | Ciclos |

| BLE opr | REL              | 93     | rr          | 3      |

### BLO - Bifurcación si es más Menor

(Lo mismo que la instrucción BCS)

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si(C) = 1

por ejemplo, si (ACCA) < (M) (números binarios sin signo)

**Descripción**: Si la instrucción BLO se ejecuta inmediatamente después de la ejecución de una instrucción CMP o SUB, la bifurcación ocurrirá si el número binario sin signo en ACCA era menor del número binario sin signo en M. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Ciclos |   |

|-----------|------------------|--------|--------|---|

| Fuente    | Direccionamiento | Opcode |        |   |

| BLO (rel) | REL              | 25     | rr     | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Complementa        | rio  | Bifurcación | Comentario    |

|--------------|-----------|-----------|--------|--------------------|------|-------------|---------------|

| r > m        | C + Z = 0 | BHI       | 22     | R ≤ m              | BLS  | 23          | Sin signo     |

| r ≥ m        | C = 0     | BHS/BCC   | 24     | R < m              | BLO/ | 25          | Sin signo     |

|              |           |           |        |                    | BCS  |             |               |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m              | BNE  | 26          | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m              | BHI  | 22          | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | R≥m                | BHS/ | 24          | Sin signo     |

|              |           |           |        |                    | BCC  |             |               |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo        | BCC  | 24          | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0              | BNE  | 26          | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más                | BPL  | 2A          | Simple        |

| I            | I = 1     | BMS       | 2D     | I                  | BMC  | 2C          | Simple        |

| Enmascarable |           |           |        | Enmascarable = $0$ |      |             |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio           | BHC  | 28          | Simple        |

| Acarreo      |           |           |        | Acarreo            | C    |             |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo           | BIL  | 2E          | Simple        |

| Siempre      | _         | BRA       | 20     | Nunca              | BRN  | 21          | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BLS - Bifurcación si es Menor o Igual

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si[(C) + (Z)] = 1

por ejemplo, si  $(ACCA) \le (M)$  (números binarios sin signo)

**Descripción**: Causa una bifurcación si C o Z se pone a 1. Si la instrucción BLS se ejecuta inmediatamente después de la ejecución de una instrucción CMP o SUB, la bifurcación ocurrirá si el número binario sin signo en ACCA fue menor o igual al número binario sin signo en M. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Ciclos |   |

|-----------|------------------|--------|--------|---|

| Fuente    | Direccionamiento | Opcode |        |   |

| BLS (rel) | REL              | 23     | rr     | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Complementario     |         | Bifurca | Comentario    |

|--------------|-----------|-----------|--------|--------------------|---------|---------|---------------|

|              |           |           |        |                    |         | ción    |               |

| r > m        | C + Z = 0 | BHI       | 22     | $R \leq m$         | BLS     | 23      | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | $R \le m$          | BLO/BCS | 25      | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m              | BNE     | 26      | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m              | BHI     | 22      | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$          | BHS/BCC | 24      | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo        | BCC     | 24      | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0              | BNE     | 26      | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más                | BPL     | 2A      | Simple        |

| I            | I = 1     | BMS       | 2D     | I                  | BMC     | 2C      | Simple        |

| Enmascarable |           |           |        | Enmascarable = $0$ |         |         | _             |

| Medio        | H = 1     | BHCS      | 29     | No Medio           | BHCC    | 28      | Simple        |

| Acarreo      |           |           |        | Acarreo            |         |         |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo           | BIL     | 2E      | Simple        |

| Siempre      | _         | BRA       | 20     | Nunca              | BRN     | 21      | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BLT - Bifurcación si es Menor que (Operandos con signo)

Operación:  $PC \leftarrow (PC) + \$0002 + rel$  si  $Z(N \oplus V) = 1$

Por ejemplo, si (A) < (M) (números complemento a dos con signo)

**Descripción:** Si la instrucción BLT se ejecuta inmediatamente después de la ejecución de una instrucción CMP, CPX, CPHX o SUB, la bifurcación ocurrirá si y sólo si, el número complemento a dos representado por el registro interno apropiado (A, X o H:X) era menor que o igual al número complemento a dos representado por M

#### Códigos de condición y Formula Boleana

| Código  | Modo de          | Cód    | HC08        |        |

|---------|------------------|--------|-------------|--------|

| Fuente  | Direccionamiento | Opcode | Operando(s) | Ciclos |

| BLT opr | REL              | 91     | rr          | 3      |

## BMC - Bifurcación si la Máscara de Interrupción es 0

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si I = 0

**Descripción**: Prueba el estado del bit I en el CCR y causa una bifurcación si I es cero (por ejemplo, si se habilitan las interrupciones). Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Ciclos |   |

|-----------|------------------|--------|--------|---|

| Fuente    | Direccionamiento | Opcode |        |   |

| BMC (rel) | REL              | 2C     | rr     | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Complem      | Complementario |      | Comentario    |

|--------------|-----------|-----------|--------|--------------|----------------|------|---------------|

|              |           |           |        |              |                | ción |               |

| r > m        | C + Z = 0 | BHI       | 22     | $R \le m$    | BLS            | 23   | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | R < m        | BLO/BCS        | 25   | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m        | BNE            | 26   | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m        | BHI            | 22   | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | R≥m          | BHS/BCC        | 24   | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo  | BCC            | 24   | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0        | BNE            | 26   | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más          | BPL            | 2A   | Simple        |

| I            | I = 1     | BMS       | 2D     | I            | BMC            | 2C   | Simple        |

| Enmascarable |           |           |        | Enmascarable |                |      | _             |

|              |           |           |        | =0           |                |      |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio     | BHCC           | 28   | Simple        |

| Acarreo      |           |           |        | Acarreo      |                |      |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo     | BIL            | 2E   | Simple        |

| Siempre      |           | BRA       | 20     | Nunca        | BRN            | 21   | Incondicional |

r = registro (ACCA o X); m = operando memoria

### BMI - Bifurcación si es Menor

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si(N) = 1

**Descripción:** Prueba que el estado del bit N en el CCR y causa una bifurcación si N es 1. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Có    | digo  | Modo de          | Códig  | Ciclos |   |

|-------|-------|------------------|--------|--------|---|

| Fu    | ente  | Direccionamiento | Opcode |        |   |

| BMI ( | (rel) | REL              | 2B     | rr     | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Complementario |         | Bifurca | Comentario    |

|--------------|-----------|-----------|--------|----------------|---------|---------|---------------|

|              |           |           |        |                |         | ción    |               |

| r > m        | C + Z = 0 | BHI       | 22     | R ≤ m          | BLS     | 23      | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | R < m          | BLO/BCS | 25      | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m          | BNE     | 26      | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m          | BHI     | 22      | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | R≥m            | BHS/BCC | 24      | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo    | BCC     | 24      | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0          | BNE     | 26      | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más            | BPL     | 2A      | Simple        |

| I            | I = 1     | BMS       | 2D     | I              | BMC     | 2C      | Simple        |

| Enmascarable |           |           |        | Enmascarable   |         |         | _             |

|              |           |           |        | = 0            |         |         |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio       | BHCC    | 28      | Simple        |

| Acarreo      |           |           |        | Acarreo        |         |         |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo       | BIL     | 2E      | Simple        |

| Siempre      |           | BRA       | 20     | Nunca          | BRN     | 21      | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BMS - Bifurcación si la Máscara de Interrupción es 1

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si (I) = 1

**Descripción**: Prueba el estado del bit I en el CCR y causa una bifurcación si I es 1 (por ejemplo, si las interrupciones son inválidas). Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código             | Ciclos |   |

|-----------|------------------|--------------------|--------|---|

| Fuente    | Direccionamiento | Opcode Operando(s) |        |   |

| BMS (rel) | REL              | 2D                 | rr     | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Complementario |         | Bifurca | Comentario    |

|--------------|-----------|-----------|--------|----------------|---------|---------|---------------|

|              |           |           |        |                |         | ción    |               |

| r > m        | C + Z = 0 | BHI       | 22     | $R \leq m$     | BLS     | 23      | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | $R \le m$      | BLO/BCS | 25      | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m          | BNE     | 26      | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m          | BHI     | 22      | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$      | BHS/BCC | 24      | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo    | BCC     | 24      | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | $R \neq 0$     | BNE     | 26      | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más            | BPL     | 2A      | Simple        |

| I            | I = 1     | BMS       | 2D     | I              | BMC     | 2C      | Simple        |

| Enmascarable |           |           |        | Enmascarable   |         |         |               |

|              |           |           |        | = 0            |         |         |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio       | BHCC    | 28      | Simple        |

| Acarreo      |           |           |        | Acarreo        |         |         |               |

| IRQ Pin Alto |           | BIH       | 2F     | IRQ Bajo       | BIL     | 2E      | Simple        |

| Siempre      |           | BRA       | 20     | Nunca          | BRN     | 21      | Incondicional |

r = registro (ACCA o X); m = operando memoria

## BNE - Bifurcación si no es Igual

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si(Z) = 0

**Descripción:** Prueba el estado del bit Z en el CCR y provoca una bifurcación si Z está a 0. Siguiendo una instrucción de comparación o substracción, la instrucción BEQ provocará una bifurcación si los argumentos no serán iguales. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

#### Códigos de condición y Formula Boleana

#### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código             | Ciclos |   |

|-----------|------------------|--------------------|--------|---|

| Fuente    | Direccionamiento | Opcode Operando(s) |        |   |

| BNE (rel) | REL              | 26                 | rr     | 3 |

| Prueba       | Boole     | Mnemónico | Opcode | Complementario |         | Bifurca | Comentario    |

|--------------|-----------|-----------|--------|----------------|---------|---------|---------------|

|              |           |           |        |                |         | ción    |               |

| r > m        | C + Z = 0 | BHI       | 22     | $R \leq m$     | BLS     | 23      | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | $R \le m$      | BLO/BCS | 25      | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | $R \neq m$     | BNE     | 26      | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m          | BHI     | 22      | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$      | BHS/BCC | 24      | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo    | BCC     | 24      | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0          | BNE     | 26      | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más            | BPL     | 2A      | Simple        |

| I            | I = 1     | BMS       | 2D     | I              | BMC     | 2C      | Simple        |

| Enmascarable |           |           |        | Enmascarable   |         |         |               |

|              |           |           |        | =0             |         |         |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio       | BHCC    | 28      | Simple        |

| Acarreo      |           |           |        | Acarreo        |         |         |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo       | BIL     | 2E      | Simple        |

| Siempre      |           | BRA       | 20     | Nunca          | BRN     | 21      | Incondicional |

r = registro (ACCA o X); m = operando memoria

# **BPL** - Bifurcación si es Positivo

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$  Si(N) = 0

**Descripción**: Prueba el estado del bit N en el CCR y provoca una bifurcación si N está a 0. Véase la instrucción BRA para más detalles de la ejecución de la bifurcación.

# Códigos de condición y Formula Boleana

## Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Máquina | Ciclos |

|-----------|------------------|--------|---------|--------|

| Fuente    | Direccionamiento | Opcode |         |        |

| BPL (rel) | REL              | 2A     | rr      | 3      |

Esta tabla es un resumen de todas las instrucciones de bifurcación.

| Prueba       | Boole     | Mnemónico | Opcode | Complementario |         | Bifurca | Comentario    |

|--------------|-----------|-----------|--------|----------------|---------|---------|---------------|

|              |           |           |        |                |         | ción    |               |

| r > m        | C + Z = 0 | BHI       | 22     | $R \leq m$     | BLS     | 23      | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | $R \le m$      | BLO/BCS | 25      | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | $R \neq m$     | BNE     | 26      | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m          | BHI     | 22      | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$      | BHS/BCC | 24      | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo    | BCC     | 24      | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0          | BNE     | 26      | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más            | BPL     | 2A      | Simple        |

| I            | I = 1     | BMS       | 2D     | I              | BMC     | 2C      | Simple        |

| Enmascarable |           |           |        | Enmascarable   |         |         |               |

|              |           |           |        | =0             |         |         |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio       | BHCC    | 28      | Simple        |

| Acarreo      |           |           |        | Acarreo        |         |         |               |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo       | BIL     | 2E      | Simple        |

| Siempre      |           | BRA       | 20     | Nunca          | BRN     | 21      | Incondicional |

r = registro (ACCA o X); m = operando memoria

# **BRA** - Bifurcación Incondicional

Operación:  $PC \leftarrow (PC) + \$0002 + Rel$

**Descripción:** Bifurcación incondicional a la dirección dada por la fórmula anterior, en qué 'Rel' es el desplazamiento relativo guardado como un número complemento a dos en el último byte de código máquina correspondiente a la instrucción de bifurcación. PC es la dirección del 'opcode' para la instrucción bifurcación.

El programa fuente especifica el destino de cualquier instrucción de bifurcación por su dirección absoluta o como un valor numérico o como un símbolo o expresión que puede ser evaluada numéricamente por el ensamblador. El ensamblador calcula la dirección relativa 'Rel' de la dirección absoluta y el valor actual de la posición del contador.

### Códigos de condición y Formula Boleana

Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Máquina | Ciclos |

|-----------|------------------|--------|---------|--------|

| Fuente    | Direccionamiento | Opcode |         |        |

| BRA (rel) | REL              | 20     | rr      | 3      |

Esta tabla es un resumen de todas las instrucciones de bifurcación.

| Prueba       | Boole     | Mnemónico | Opcode | Complementario |         | Bifurca | Comentario    |

|--------------|-----------|-----------|--------|----------------|---------|---------|---------------|

|              |           |           |        |                |         | ción    |               |

| r > m        | C + Z = 0 | BHI       | 22     | $R \le m$      | BLS     | 23      | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | R < m          | BLO/BCS | 25      | Sin signo     |

| r = m        | Z = 1     | BEQ       | 27     | R ≠ m          | BNE     | 26      | Sin signo     |

| r≤ m         | C + Z = 1 | BLS       | 23     | R > m          | BHI     | 22      | Sin signo     |

| r < m        | C = 1     | BLO/BCS   | 25     | $R \ge m$      | BHS/BCC | 24      | Sin signo     |

| Acarreo      | C = 1     | BCS       | 25     | Sin Acarreo    | BCC     | 24      | Simple        |

| r = 0        | Z = 1     | BEQ       | 27     | r ≠ 0          | BNE     | 26      | Simple        |

| Negativo     | N = 1     | BMI       | 2B     | Más            | BPL     | 2A      | Simple        |

| I            | I = 1     | BMS       | 2D     | I              | BMC     | 2C      | Simple        |

| Enmascarable |           |           |        | Enmascarable   |         |         |               |

|              |           |           |        | =0             |         |         |               |

| Medio        | H = 1     | BHCS      | 29     | No Medio       | BHCC    | 28      | Simple        |

| Acarreo      |           |           |        | Acarreo        |         |         | _             |

| IRQ Pin Alto | _         | BIH       | 2F     | IRQ Bajo       | BIL     | 2E      | Simple        |

| Siempre      |           | BRA       | 20     | Nunca          | BRN     | 21      | Incondicional |

r = registro (ACCA o X); m = operando memoria

# BRCLR n - Bifurcación si el Bit n es Cero

Operación:  $PC \leftarrow (PC) + \$0003 + Rel$  Si el bit n de M = 0

**Descripción:** Prueba el bit n (N = 7, 6, 5...0) de la posición M y bifurca si el bit se pone a 0, M puede ser una posición de RAM o una dirección del registro de E/S en el área de memoria \$0000 a \$00FF (por ejemplo, modo de direccionamiento directo si está usado para especificar la dirección del operando).

El bit C es 1 para el estado de prueba de bit. Cuando se usa junto con una apropiada instrucción de rotación, BRCLR n mantiene un método fácil realizando sesiones de serie a paralelo.

### Códigos de condición y Formula Boleana

| Código Fuente | Modo de          | Códi   | Ciclos      |   |

|---------------|------------------|--------|-------------|---|

|               | Direccionamiento | Opcode | Operando(s) |   |

| BRCLR 0,(opr) | DIR (bit 0)      | 01     | dd rr       | 5 |

| BRCLR 1,(opr) | DIR (bit 1)      | 03     | dd rr       | 5 |

| BRCLR 2,(opr) | DIR (bit 2)      | 05     | dd rr       | 5 |

| BRCLR 3,(opr) | DIR (bit 3)      | 07     | dd rr       | 5 |

| BRCLR 4,(opr) | DIR (bit 4)      | 09     | dd rr       | 5 |

| BRCLR 5,(opr) | DIR (bit 5)      | 0B     | dd rr       | 5 |

| BRCLR 6,(opr) | DIR (bit 6)      | 0D     | dd rr       | 5 |

| BRCLR 7,(opr) | DIR (bit 7)      | 0F     | dd rr       | 5 |

# **BRN** - Nunca Bifurcación

Operación:  $PC \leftarrow (PC) + \$0002$

**Descripción**: Nunca hace bifurcación. En efecto, esta instrucción puede ser considerada como 2-bytes NOP (no operación) requiriendo tres ciclos para su ejecución. Esta inclusión en el juego de instrucciones es para mantener un complemento de la instrucción BRA. La instrucción es útil durante el programa de depuración para negar el efecto de otra instrucción de bifurcación sin perturbar el byte de desplazamiento.

### Códigos de condición y Formula Boleana

### Forma, Modos de Direccionamiento, Código Máquina y Ciclos

| Código    | Modo de          | Código | Máquina | Ciclos |

|-----------|------------------|--------|---------|--------|

| Fuente    | Direccionamiento | Opcode |         |        |

| BRN (rel) | REL              | 21     | rr      | 3      |

Esta tabla es un resumen de todas las instrucciones de bifurcación.

| Prueba       | Boole     | Mnemónico | Opcode | Complementario |         | Bifurca | Comentario    |

|--------------|-----------|-----------|--------|----------------|---------|---------|---------------|

|              |           |           |        |                |         | ción    |               |

| r > m        | C + Z = 0 | BHI       | 22     | $R \leq m$     | BLS     | 23      | Sin signo     |

| $r \ge m$    | C = 0     | BHS/BCC   | 24     | $R \le m$      | BLO/BCS | 25      | Sin signo     |